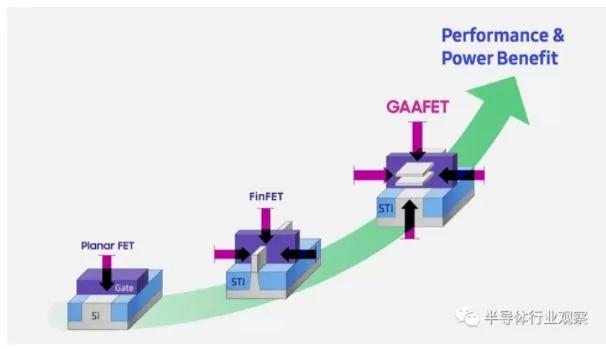

三星晶圓廠將成為第一家在即將到來的3nm工藝中使用類似全柵場效應電晶體(GAAFET)結構的半導體製造商。雖然該節點尚未準備就緒,但在IEEE國際固態電路會議(ISSCC)上,三星晶圓廠的工程師分享了有關即將推出的3 nm GAE MBCFET(multi-bridge channel FET)製造技術的一些細節。

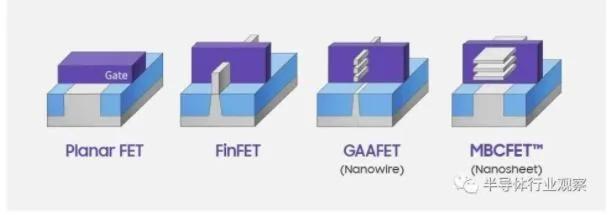

據介紹,有兩種類型的GAAFET:典型的GAAFET,這被稱為具有「薄」鰭的奈米線。以及MBCFET,稱為具有「厚」鰭的奈米片。在兩種情況下,柵極材料在所有側面上都圍繞溝道區。奈米線和奈米片的實際實現方式在很大程度上取決於設計,因此,一般而言,許多行業觀察家用術語GAAFET來描述兩者。但是以前它們被稱為環繞柵電晶體(surrounding-gate transistors :SGT)。值得一提的是,MBCFET是 三星的 商標。

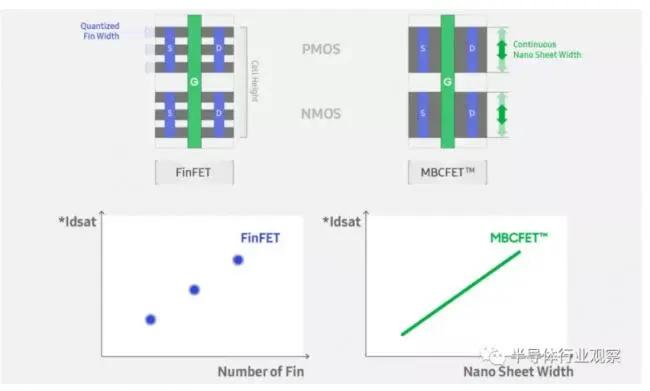

1988年,全球首次展示了GAAFET,因此該技術的關鍵優勢眾所周知。這種電晶體的結構使得設計人員可以通過調節電晶體通道的寬度(也稱為有效寬度或Weff)來精確地對其進行調諧,以實現高性能或低功耗。較寬的薄片(sheets)可以在更高的功率下實現更高的性能,而較薄/較窄的薄片可以降低功耗和性能。為了對FinFET做類似的事情,工程師必須使用額外的鰭來改善性能。但是在這種情況下,電晶體溝道的「寬度」只能增加一倍或兩倍,這並不是很精確,有時效率很低。另外,由於不同的電晶體可以用於不同的目的,因此通過調整GAAFET可以提高電晶體的密度。

(圖片來源:三星)

(圖片來源:三星)

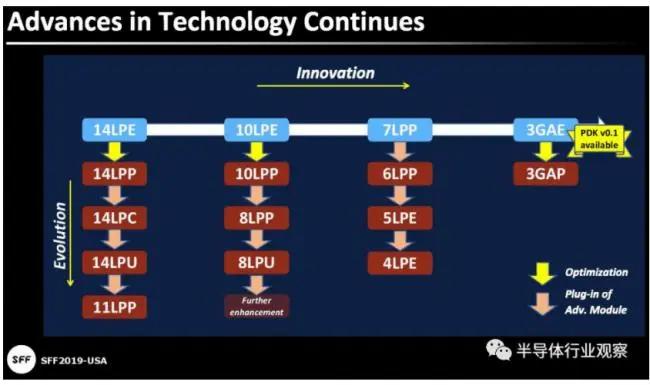

早在2019年,三星推出的3GAE工藝設計套件版本0.1就包括四種不同的奈米片寬度,以為早期採用者提供一定的靈活性,儘管目前尚不清楚該公司是否增加了寬度以提供額外的靈活性。但是三星表示,總的來說,與7LPP技術相比,其3GAE節點將使性能提高30%(在相同的功率和複雜度下),功耗降低50%(在相同的時鐘和複雜度下),並且電晶體密度提高了80%(包括邏輯和SRAM電晶體的混合)。

(圖片來源:三星)

三星的3GAE(其第一代MBCFET技術)將於2022年推出。雖然三星目前尚未披露其所有特性。但該公司在ISSCC上討論了如何使用新型電晶體來提高SRAM性能和可擴展性。

近年來,SRAM的可擴展性一直落後於邏輯的可擴展性。同時,現代片上系統將SRAM的負載用於各種快取記憶體,因此提高其可伸縮性是一項至關重要的任務。

(圖片來源:三星)

據《EE Times》亞洲報導,三星代工廠在ISSCC上介紹了其256Mb MBCFET SRAM晶片,該晶片的尺寸為56mm2 。這意味著儘管該公司尚未推出其首款3GAE邏輯晶片,但顯然該技術適用於SRAM。

SRAM是一個六電晶體存儲單元:兩個傳輸門(pass gates),兩個上拉和兩個下拉。在FinFET設計中,SRAM單元將使用具有相同溝道寬度的相同電晶體。藉助MBCFET,三星可以調整溝道寬度,因此提出了兩種方案:在一種情況下,三星將溝道更寬的電晶體用於傳輸門和下拉電路,而在另一種情況下,三星將使用具有較寬溝道的電晶體用於傳輸門和電晶體。

至於較窄的下拉通道。三星通過IEEE Spectrum稱,通過將具有更寬溝道的電晶體用於傳輸門,並將具有較窄通道的電晶體用於上拉,與常規的SRAM單元相比,三星設法將寫入電壓降低了230 mV 。